Projects & Portfolio

rfproto Python Library

rfproto is a Python library for RF and SDR prototyping. It contains helpful reuse methods for RF measurements, as well as experimenting with topics like communication systems, radar, antenna arrays, etc.

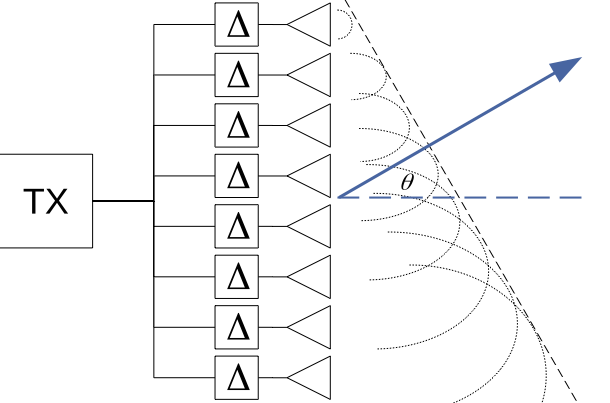

FPGA-Based ADBF Using ML for MIMO Systems

This Masters Thesis research shows the development of a novel Deep Learning model (CNN), trained to perform Adaptive Digital Beamforming. The model was shown to vastly outperform the current state-of-the-art Adaptive Digital Beamforming FPGA implementation, with a 10x decrease in latency and a 10x decrease in programmable logic resource utilization.

4-Channel RF Diplexer Front End

An open-source (KiCAD) RF front end with 4 independent RX & TX channels optimized for MIMO/Radar prototyping. It implements an I2C bus for digital control of each channel’s attenuation and single-ended control of T/R switch for fast action. A switch-mode power supply and separate low dropout regulators for each channel are utilized to provide low-ripple power to RF Low Noise Amplifiers.

FlexRIO Peer-to-Peer GPU

NI FlexRIO driver and example CUDA/C++/FPGA code for implementing peer-to-peer (P2P) data streams between a National Instruments FlexRIO device and a NVIDIA GPU using a zero-copy, bidirectional, DMA communication path via GPUDirect kernel driver.

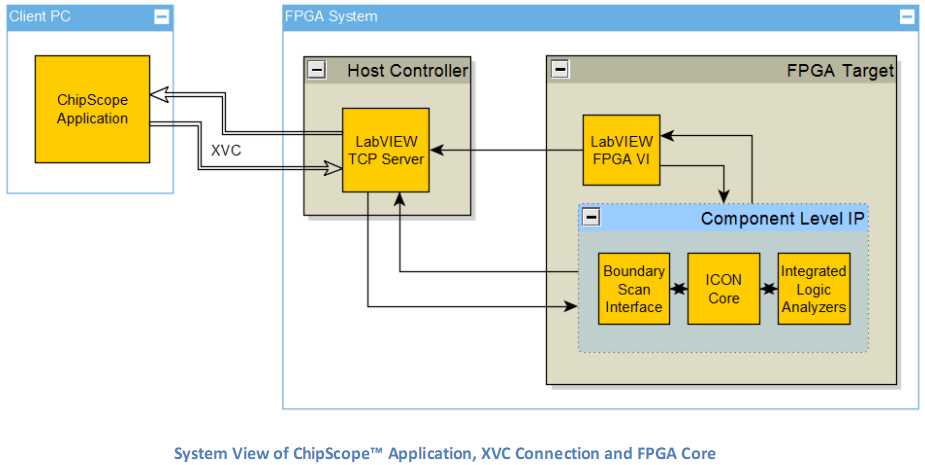

Remote Debug with XVC

Whitepaper and VHDL example code on how to incorporate Integrated Logic Analyzers (ILA) into a design and perform remote JTAG debugging using the Xilinx Virtual Cable (XVC) protocol on a LabVIEW TCP/IP server that is bus-connected to the FPGA to access JTAG as memory-mapped registers.

High-Speed Stream-to-Disk

This LabVIEW and FPGA example shows best practices for efficient streaming data to disk/RAID with the lowest overhead and highest data rates over PCIe.